数据流程

简单来说,就是把芯片设计图纸(bushi)交给代工厂(Fab),然后Fab再去根据图纸制作掩模,开始生产。

当然,IC设计公司提交的肯定不是大家想象的那种图纸。因为集成电路的元器件太小,动辄以nm来衡量;数量又很多,手机soc的晶体管数量可以高达百亿级别。

如果放大画到纸上,需要的图纸将是天文数字,画出来费时费力,而且校准修订图纸也十分复杂。因此靠“画”图纸,是非常不现实的。如果一块芯片含有36亿个晶体管,即使画一个晶体管只需要一秒钟,那也需要36亿/86400/365=114年

不过早期(60年代)的微电子工程师,的确通过手工绘制电路图。因为此时的集成电路规模不大,器件尺寸也较大。此前有传言,由于长期伏案绘图,资深的工程师胸前都会被桌子的边缘搁出印子来。根据胸口的印记,可以判断出此人的工作经验

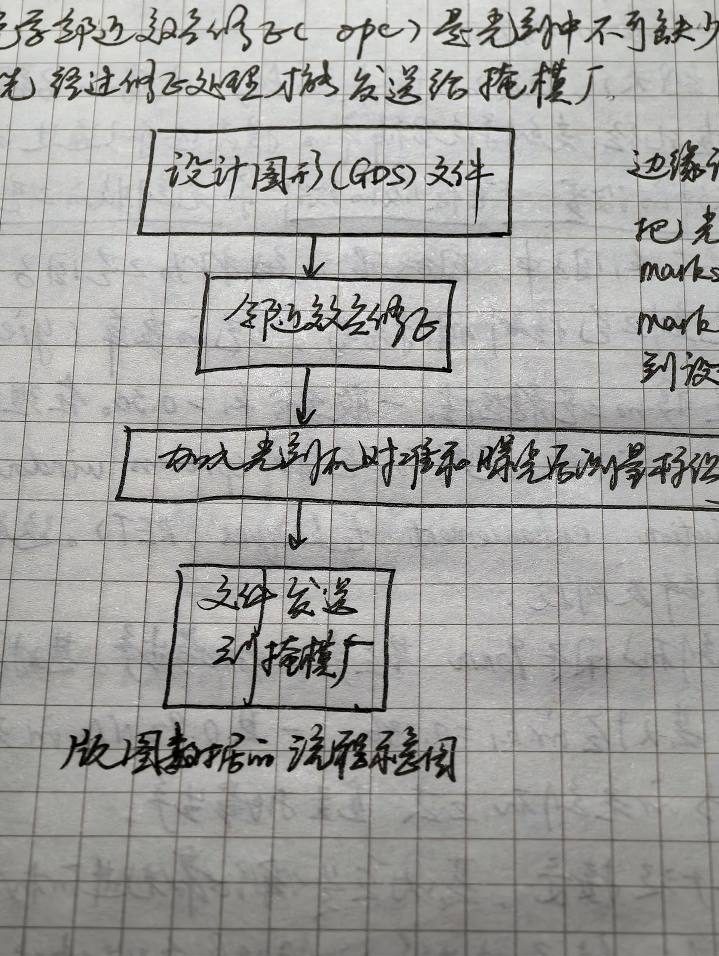

IC公司提交给Fab的是设计图形(GDS)文件。设计的版图(layout)后续要对版图进行处理,以消除光学临近效应(optical proximity effect,OPE)。这是因为曝光过程中,图形或多或少存在畸变,需要进行补偿。很好理解,用模具铸造金属的时候,多多少少也会留个缝隙对吧,不会完全一致。

消除邻近效应之后,需要在掩模上加入用于光刻机对准的标识。

然后才能把文件发给掩模厂,制备掩模,投入生产中去。

缺陷检测

光刻图形的缺陷是指任何对目标图形的偏离。用大白话举例,比如说我希望某处有一个晶体管,但是晶体管偏移了位置,导致某处没有晶体管。这就是缺陷。

由于光刻流程很长,因此缺陷的来源也存在多种途径。

一是光刻材料的问题,比如说光刻胶里面进灰了或者过期变质了;

二是设备问题,比如机器内的灰尘掉落在晶圆的表面;

三是工艺问题,比如曝光的时候对准存在偏差。

缺陷检测可以分为两部分来进行:一是在晶圆表面涂胶之后,对表面的颗粒物进行检测;另一个则是在曝光之后,对图形进行缺陷检测。

涂胶后的缺陷检测

怎么检测晶圆表面的光刻胶上是否有缺陷了,答案当然是用眼睛去看开个玩笑,肉眼是很难看出细小颗粒物的,需要用到空白晶圆检测仪。仪器的原理是一束光照射在晶圆表面,有颗粒的地方和无颗粒的地方反光强度不一样,由此可以确定暗处或者亮点处为缺陷。根据入射光与晶圆的角度不同,可以分为暗场检测和亮场检测。前者视场为暗色,缺陷为亮色;后者视场为亮色,缺陷相对较暗。

检测仪记录下缺陷的坐标后,可以用电子显微镜或者原子力显微镜对缺陷做进一步的形状和成分分析。

曝光后的缺陷检测

这部分原理很简单,检测设备分析每一个曝光区域的图形,然后与相邻的曝光图形做比较,不一样的地方就是缺陷。

不过有的缺陷藏在介电材料下方,而电子显微镜发射的电子束无法穿透介电材料,因此有时会出现检测出了缺陷,但是用电镜看不到的情况。这时,原子力显微镜就又该登场了。

成本

为什么高通骁龙888/8gen1宁可连用两代垃圾的三星工艺,也不愿意去找台积电下订单?台积电的产能是一方面,主要原因可能还是三星工艺的低成本吧?

一种工艺能否量产,不仅取决于技术指标,更取决于它的成本。如果台积电工艺的价格在后面加个零,恐怕少有公司会采用吧?

一枚芯片的造价,大概三到四成用在光刻部分。根据微博大佬饭统戴老板的分析,Nvidia H100的成本价可能在3000美元左右,而台积电的代工费与封装费用加起来大概是1000美元。

DUV能不能做5nm?理论上NXT2050i加上SAQP是可行的,但为什么台积电坚决要在5nm工艺引入EUV呢?当然是因为成本!EUV可以减少光刻的次数,相应的也就减少了掩模的数量和光刻胶的用量,更不必说多次曝光会导致良率降低了。

国际半导体制造协会(SEMATECH)提出了一个模型,公式如下

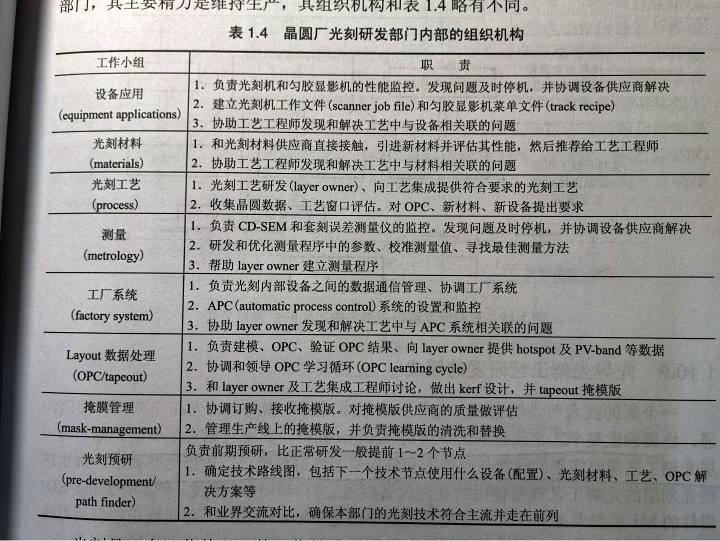

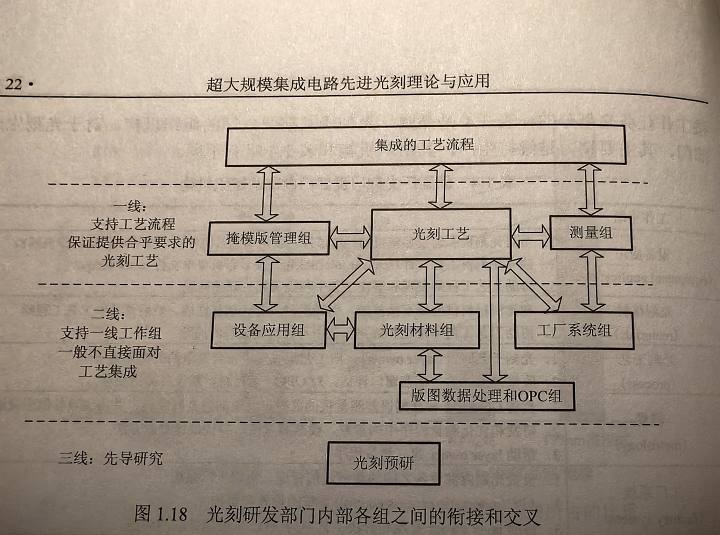

光刻工艺研发各部分的职责与协作

这几年SMIC一直被制裁,包括禁止购买设备与材料,还有今年传出来的被断了售后。去年10/7之后,长江存储和长鑫存储同样是被设备商断供,工程师一夜之间全部撤走。

这些新闻看着让人揪心,有的朋友可能会有这种想法:反正设备已经买到手了,不提供售后怎么了,大不了找别人修去。

打个不恰当的比方,就好像你的电脑坏了,Intel又不卖给你CPU,也不给你修CPU(不是修主板)。你总不能说找个店铺帮忙修吧?CPU可不是想修就修的,是很考验技术的活。

尤其是现在工艺越来越先进,工艺当中的诸多流程都不能靠Fab的工程师自己解决,需要设备商参与进来。最典型的就是ASML的EUV原型机,业界希望在70nm就用上EUV。但是后来的故事大家也知道,直到2019年,台积电量产n7+,这才用上EUV。而EUV的原型机在10年前就已经开始测试了。台积电想研发EUV,如果ASML不配合,那也是没法子的。

下图列举出Fab研发部门内部的组织结构,尤其是光刻预研(pre-development/path finder),离不开与设备商的交流。

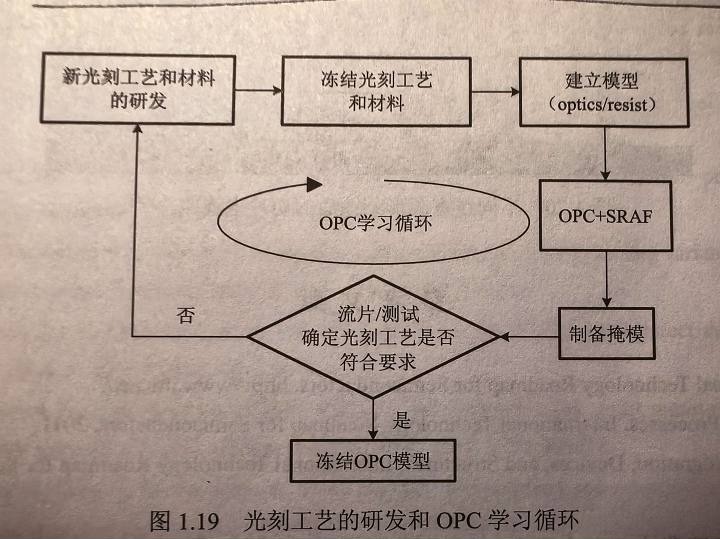

值得一提的是,研发新工艺的过程中,如果出现了更新更好的材料与设备,此前的模型也需要随之调整。经过3-4次OPC学习循环之后,新的技术节点也就大功告成。

之前有朋友提过,台积电的先进工艺是两个团队同时推进,如果某个方案遇挫,planB可以随时顶上。如果某个方案优先出成果,那么另一个团队也会立即加入。因此台积电能够在先进工艺独领风骚,也就不足为奇了。

到这里,光刻工艺的一些流程就介绍的差不多了。相信通过这几篇文章,大家一定会有所收获。但是文章还没结束,下周我将更新本系列的终章——EUV。