前文

华为突然宣布开售Mate 60 Pro,作为华为时隔两年半零四个月再度发布的5只因旗舰,刚一上市就引发极大的关注。而其搭载的新麒麟芯片,更是万众瞩目。由于华为暂时还没有开发布会介绍具体信息,因此这颗芯片的信息可以说是扑朔迷离。

暂且称它为麒麟9000S吧,根据知名媒体techinsights的说法,这颗soc是由中芯国际(SMIC)n+2工艺生产,这是继去年用n+1工艺代工MinerVa矿机芯片之后,又一次大批量生产7nm级的芯片,是值得称赞的成就。因为我始终认为,科学技术不能只摆在书架和实验室,而应该走上货架,投身市场竞争。

扯远了,麒麟的回归无疑是振奋人心的。但是现在网上的消息鱼龙混杂,在大多数人看来,只要有了光刻机,招聘几个工程师,然后把设计图纸交给代工厂,就能批量生产芯片。

但是事实果真如此吗?我想没那么简单吧,不然的话中东地区财大气粗,为何asml依旧选择把80%的euv光刻机送到台湾省和韩国的三星?为什么大陆20年底才量产14nm,去年七月份才生产7nm的产品?抱着求真务实的态度,我花了近两百元买下这本书——《超大规模集成电路先进光刻理论与应用》。就是想了解一下,芯片到底怎么做?把硅片扔到光刻机里面曝光一下就完事了吗?光刻工艺有哪些技术难点?

背景知识

要想谈光刻技术,首先需要知道什么是光刻技术。简单来说,光刻技术就是用光化学反应(photo–chemical reaction)原理,把想要的图形“印刷”到晶圆(wafer)上的过程。这么说来,光刻工艺真不应该叫刻,应该叫印。毕竟一个一个一个晶体管(transistor),不是雕刻上去,而是光化学反应印上去的……(我此前一直以为晶体管是光刻机通过雕刻硅晶圆得到的)

有了这个最基本的认识,该提到另一个事实了。那就是下面的等式不成立:

硅片+光刻机=芯片(x)大错特错!

芯片的生产流程应该是这样的:首先需要高纯硅晶圆,对晶圆进行清洗和热氧化,然后才是光刻、刻蚀、离子注入、退火、扩散、化学气相沉积(CVD)、物理气相沉积(PVD)、化学机械研磨,然后再进行封装测试,通过测试的成品就可以包装入库,然后流入市场。

半导体技术节点

关注数码圈的朋友,对这个词不会太陌生。比如说Intel曾经一直专注于深挖14nm工艺的潜力(bushi),再比如火龙810所用的20nm等等。

这里的xx纳米是指集成电路上器件的尺寸,也就是所谓技术节点。技术节点定义不是看研发人员的心情,想怎么叫就怎么叫,而是根据权威文件国际半导体技术路线图(ITRS)来制定的。

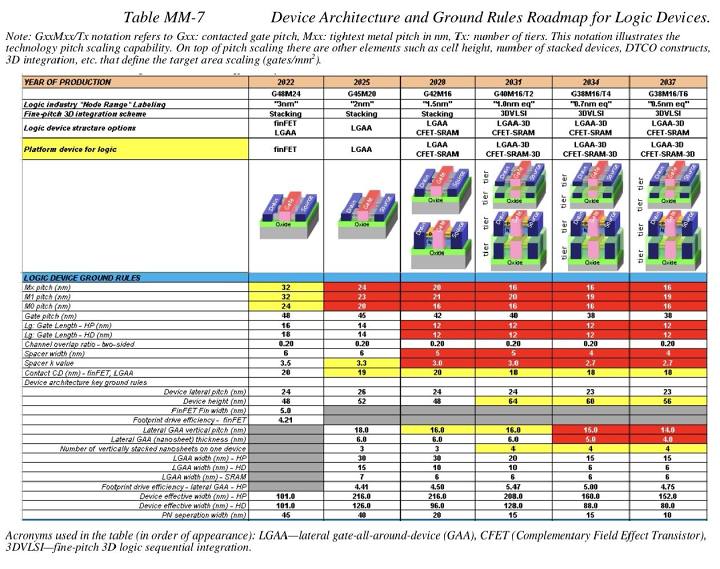

需要说明的是,集成电路可以分为逻辑器件(logic)和存储器件两大类,逻辑器件是指以互补金属氧化物半导体(CMOS)为基础的数字逻辑器件,存储器件则包括动态随机存储器(DRAM)和闪存器件(flash)。通俗一点来说就是你手机里面的soc是逻辑器件,内存和闪存则是存储器件。这两类不同的集成电路,其技术节点的定义也是不一样的。

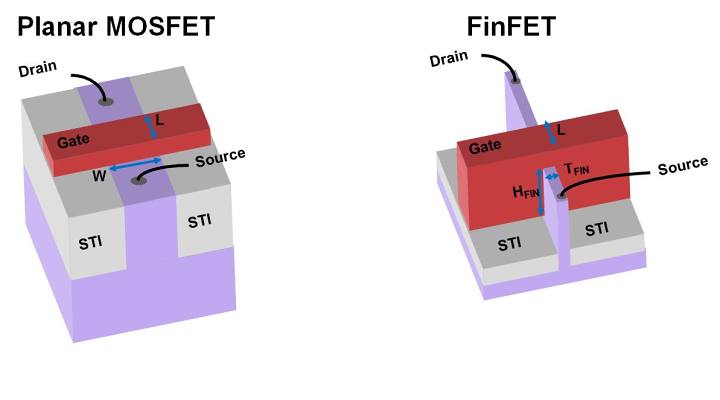

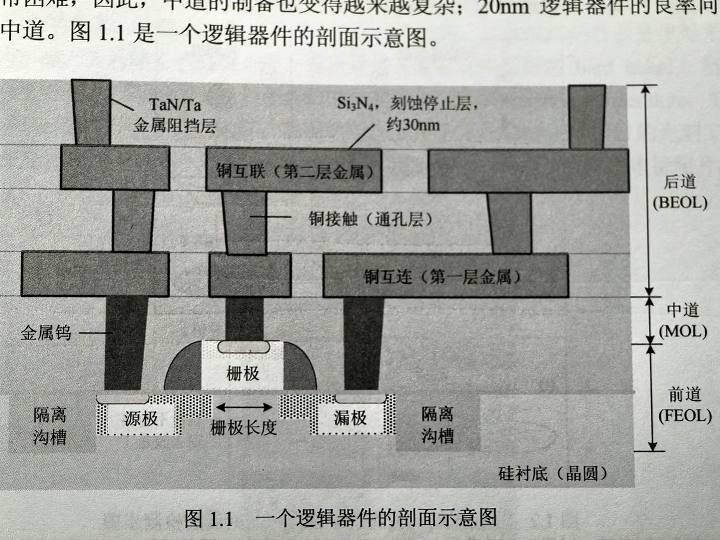

对于logic来说,一般采用栅极(gate)的长度(gate length)作为技术节点的标志。下图右侧的图形上标注的L就是length。

不过由于商业宣传等因素,现在各大半导体厂商宣传的xx nm往往不是gate length。例如Intel 10nm工艺改称Intel 7,Intel 7nm改称Intel 4。所以现在不能只看纳米前面的数字,还应该结合代工厂和晶体管密度来判断,三星5nm和台积电5nm就是天壤之别。

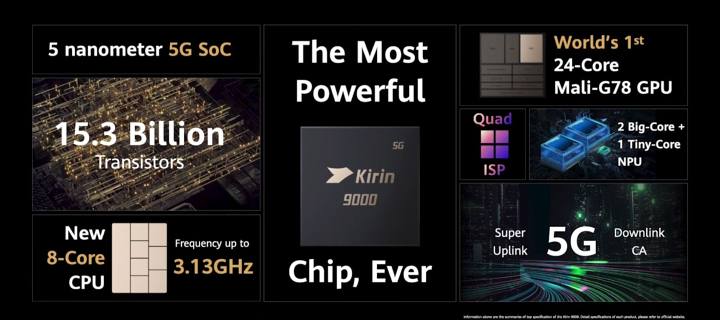

Intel 10nmSF工艺的晶体管密度是每平方毫米1亿个(100 MTr/mm²,million transistor),台积电2018年量产的N7工艺的密度是91,台积电N5的提升较大,达到了171!(原来的Intel 7nm密度为163)不过N5的171也是理论最大值,一般情况下不会用到这么高的密度。麒麟9000拥有153亿晶体管,芯片面积大约是106mm²,153/106=1.44,也就是144MTr/mm²。

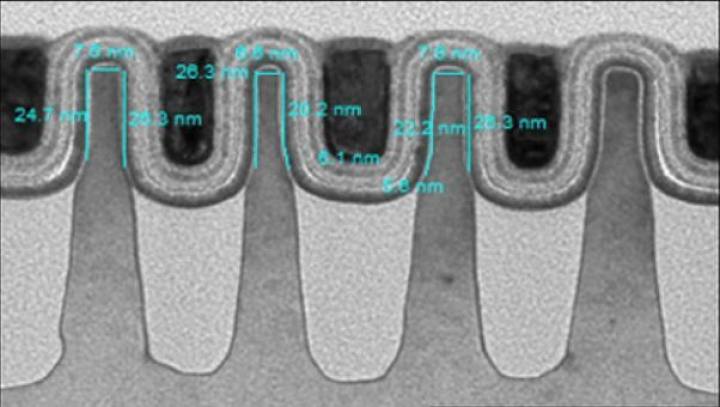

而存储器件的栅极是由一个一个一个密集的线条构成(不管是内存还是闪存),它代表了整个器件中最小的周期。

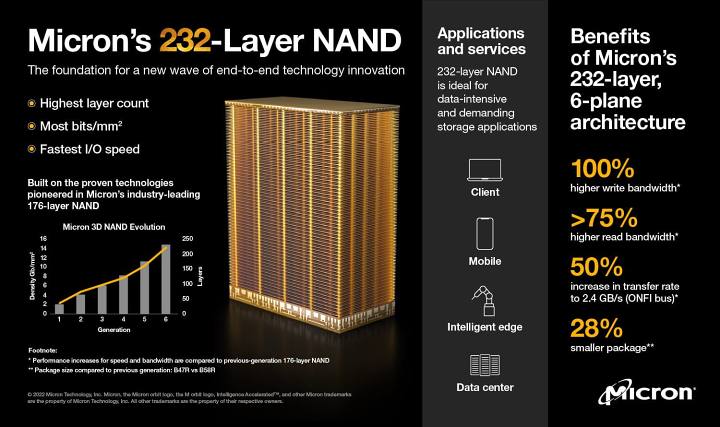

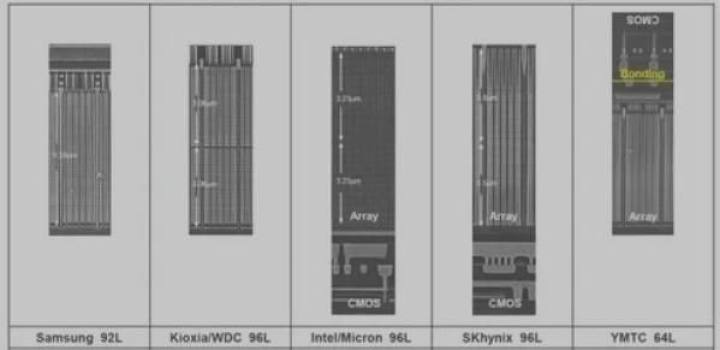

镁光232层闪存:

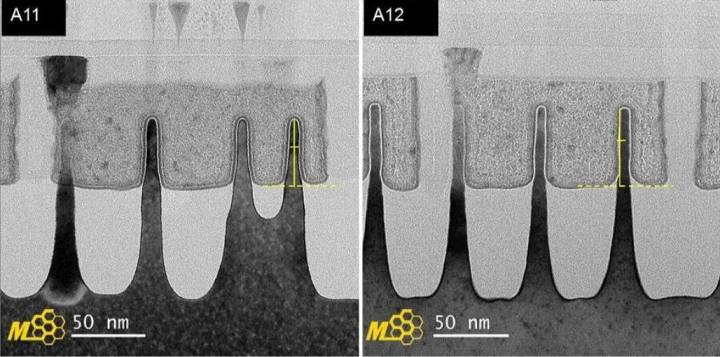

三星,铠侠/西数,Intel/镁光,海力士,长江存储:

三星的DRAM:

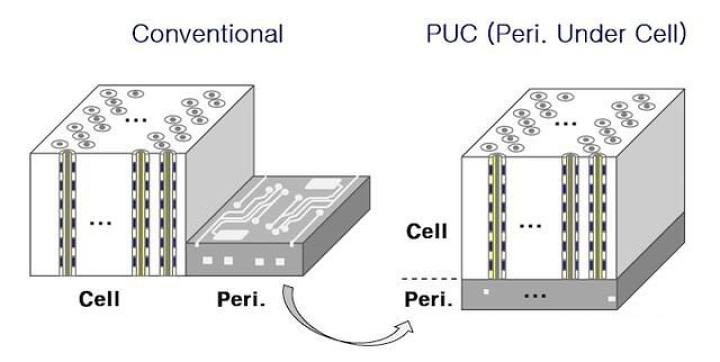

除此之外,存储器件的光刻图形有自身的特征。最明显的当属围绕着存储单元(cell)的周边图形(periphery),通俗来说就是中间是存储颗粒,四周是控制电路。

不过也有例外,那就是长江存储采用的Xtacking®晶栈®技术,将外围电路和存储单元堆叠,节约空间从而提高存储密度。

半节点

何为半节点?我先举个例子,从台积电N5到台积电N3,中间还有N4和N4P,这个N4和N4P就是半节点。

从一个技术节点到下一个技术节点,器件的关键线宽(critical dimension,CD)是按照0.7倍缩减(大概),比如三星14nm之后恰好是14*0.7≈10nm,再往后就是10*0.7=7nm。一般来说一个新技术节点的开发,需要18-24个月,正好遵循摩尔定律(Moore's law)

但是新技术节点的开发,需要新的设备、材料甚至是新的头脑。如果两年的时间内没有完成开发,而是在两年半(一坤年🐔)之后才拿出新的工艺,就会在市场竞争中落败。因此,出于市场的考虑,生产厂商会采用手头上的设备生产比现有技术节点更小的产品。

比如Intel 32nm到22nm之间的28nm,三星10nm和7nm之间夹了个8nm,台积电N5和N3中间夹了个N4。虽然半节点打不过新节点,但是可以更早投入市场。在3nm到来之前,消费者会更倾向于选择4nm芯片而不是5nm芯片。

台积电4nm

集成电路的结构与光刻层

与第一节相比,这一节的内容比较枯燥和抽象。我尽量用自己的理解,结合通俗易懂的语言快速带过。

集成电路是依靠平面工艺一层一层堆积起来的(怪不得台湾那边把集成电路叫积体电路)。对于逻辑器件来说,首先要在硅衬底上划分制备晶体管的区域(active area),然后通过离子注入实现N型和P型区域(不知道什么是N P的,自己去翻阅模电的教材),之后离子注入构成每一个晶体管的源极(source)和漏极(drain)。上述部分统称为前道工艺(FEOL)。

有前道工艺,那么当然也会有后道工艺(BEOL)。后道其实就是导线,一般来说用铜,所以后道也叫铜互联。(20年前台积电就是靠成功研发130nm铜制程,打破IBM的垄断)。

夹在前道和后道中间的当然是中道(MOL),一般是用钨或者钴把晶体管的源极、栅极、漏极和后道的第一层金属相连。由于器件的密度越来越高,中道的工艺也越来越难,半导体器件的良率问题往往发生在中道。

讲完集成电路的结构,下面来和大家交流一下光刻层。罗马不是一天建成的,芯片也不是一次光刻就能制成的。一块芯片往往需要数十次的光刻,但是光刻和光刻是不一样的。有的光刻层图形较大,有的较小。而出问题往往就发生在较小图形的光刻层上,因此又被称为关键光刻层(critical layer)。

对于一个新技术节点的光刻工艺来说,关键层需要采用新工艺和新设备,而非关键层可以沿用上一个节点的工艺和设备。例如台积电n7+工艺,非关键层没有使用euv光刻机,而是继续使用duv光刻机。